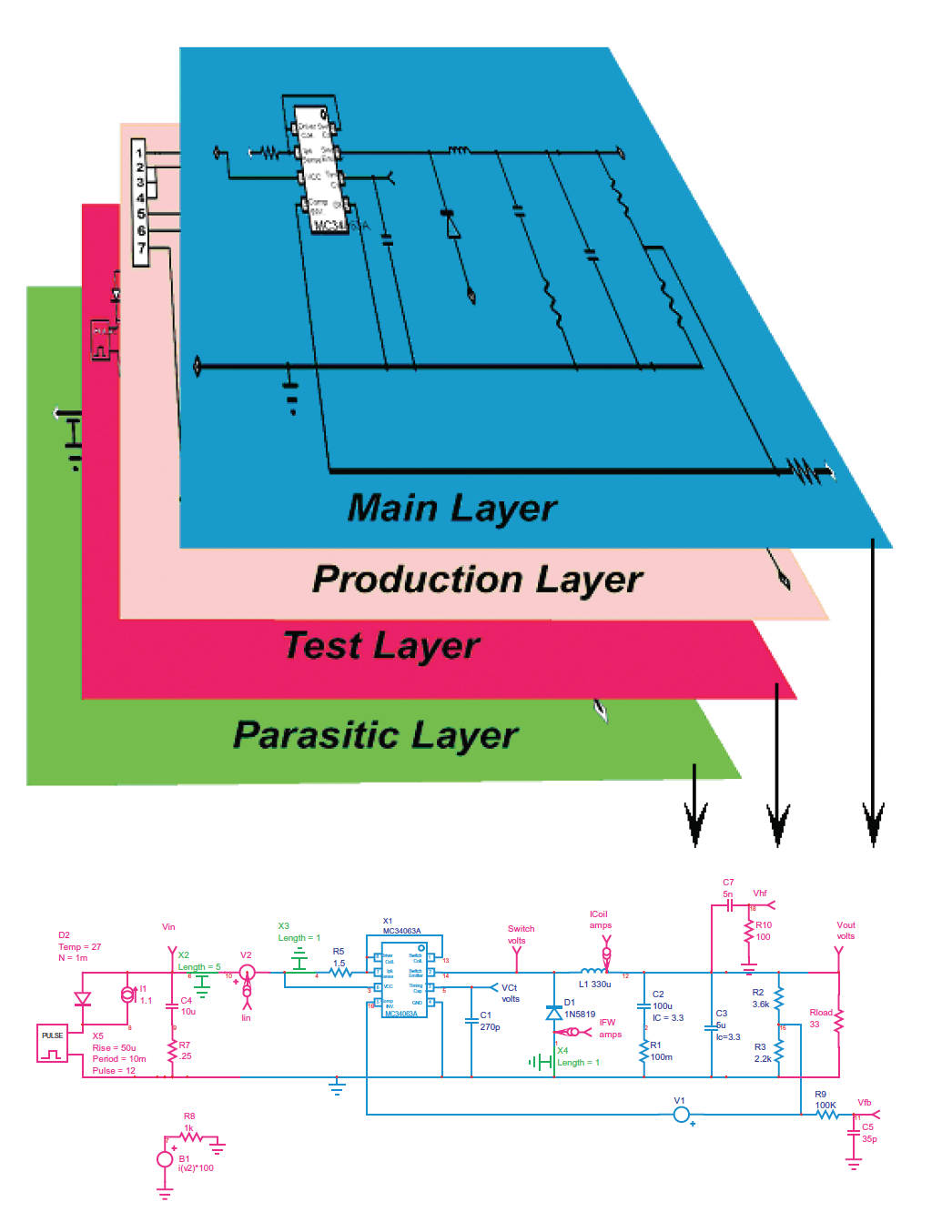

Intusoft’s Spicenet schematic editor allows for multiple layers. Various portions of the design are put on individual layers, and configurations of the schematic are defined by combinations of layers.

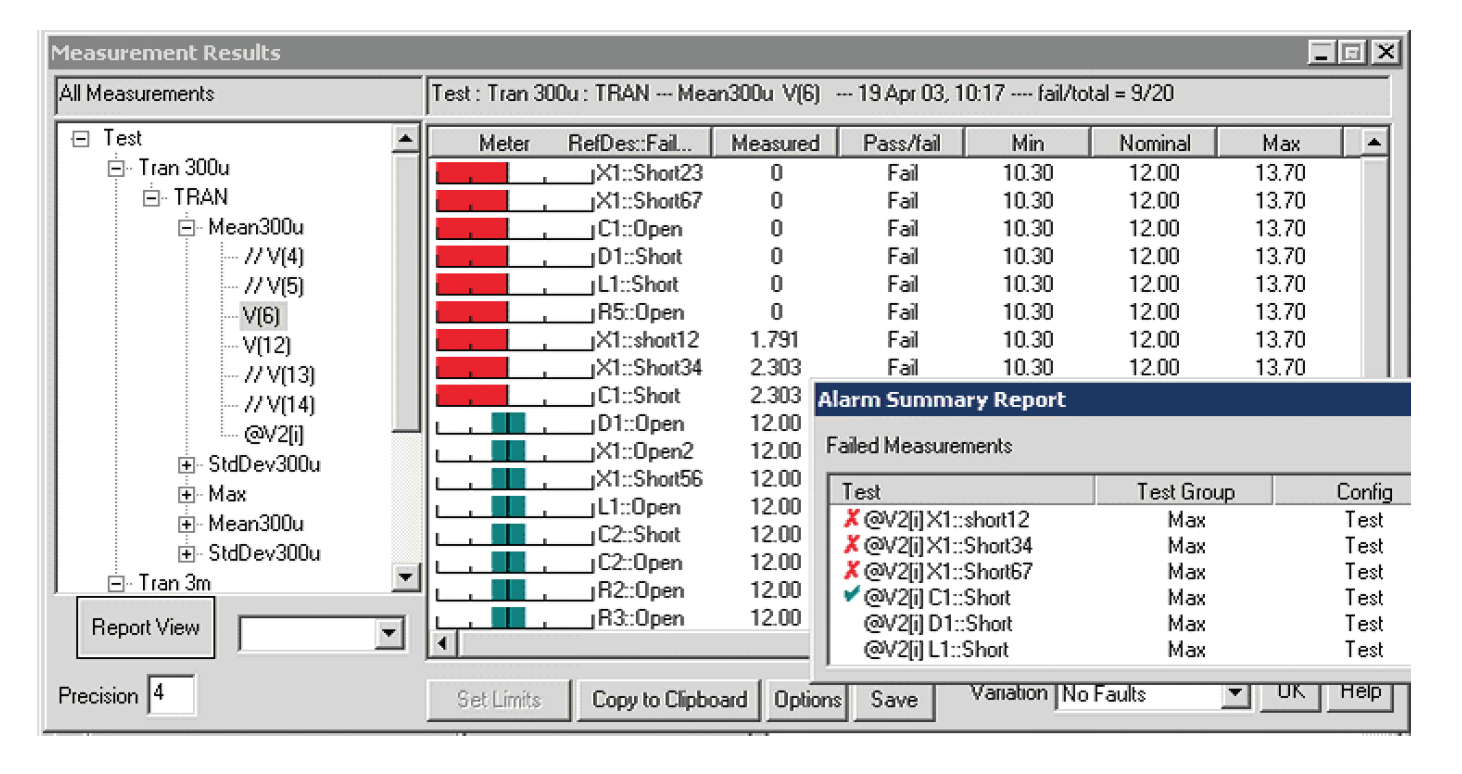

The power of multiple simulations, fault insertion, and automatic measurements provide the core capability of Test Designer. Test Designer outputs the listing of circuit faults identified by each measurement.

This advanced modeling and simulation class starts where the Introduction to ICAP/4 Windows class ends. We start by building multiple simulation settings for a design, simulate, and set up measurements. Then you will assign component variations such as tolerances and define fault conditions.

Test Designer simulates all faults in your circuit automatically, and uses the results to build a fault tree that detects the faults and isolates them to groups of replaceable components. Fault tree generation is the heart of the Test Designer technology.

Test Designer Class Content

Day 1: Schematic Entry, Simulation, Tolerances, Measurements

- Schematic Entry using layers and configurations

- Simulation Review, Settings, Waveform Viewing

- Setting up Tolerances, ICAP, Monte Carlo and Measuments

Day 2: Assigning Fault Conditions, Test Limits, Alarm Conditions

Fault Conditions:

- Logic stuck at 1 or 0

- Shorts

- Opens

Setting Test Limits

- Initial settings for measurements

- Multi-run simulations, expand limits to accommodate tolerance, supply variances, temperature

Setting Alarm Conditions and Resolving Alarms

- Identify part stress conditions

- Devise measurements to catch and group them with stress alarms

- Sequence order of tests to prevent damage to DUT

Testing Sequence, Fault-Trees, Test Synthesis and Strategy

- Stress Alarms and Simulation Failures

- Test Difficulty / Cost

- Performance Validation

- Building a Test Fault-Tree

- Test Synthesis

- Test Definition

Test Designer Training Dates and Summary

| Subject | Class Dates | Location |

|---|---|---|

| Intusoft Test Designer Training | By customer request | Customer can select location |